That shift is being shaped partly by domestic policy, with Chinese officials having spent much of the last few months urging major buyers to reduce their reliance on Nvidia hardware . That has created an opening for Cambricon and fellow domestic suppliers.

Having ambition is all well and good, but keep in mind that Cambricon doesn’t manufacture its own silicon. It depends on SMIC’s N+2 (7nm) processes for the Siyuan 590 and 690, the company’s most advanced production line that’s built entirely around DUV lithography rather than the EUV systems used by TSMC and Samsung. While N+2 can produce some pretty complex chips , it does so with a significant overhead in multi-patterning tests that raise cost and constrain performance.

This becomes apparent when you look at the numbers; Bloomberg reported yield rates of roughly 20% for Cambricon’s largest dies. That translates to four out of five chips coming off the wafer not meeting the targeted criteria, such as the chip having a defect or not meeting frequency or voltage targets (among other criteria). While some of those die could potentially be harvested for lower-power or lesser products, this yield level falls below most industry benchmarks . For instance, TSMC’s 2nm process has shown yields beyond 60% in test runs. Cambricon is therefore attempting to scale volume on a node that is both older and materially less efficient, so even if SMIC allocates more capacity, the proportion of chips that survive the manufacturing process will define the effective output.

Competition for those wafers adds another layer. Huawei, whose Ascend accelerators now form the backbone of many in-country training clusters , also relies on SMIC for advanced production. Demand for smartphone SoCs built on the same family of nodes has risen since Huawei’s return to 5G handsets. Any increase in Cambricon’s allocation requires SMIC to rebalance commitments across several strategically important customers, so the half-million-unit target for 2026 hints at strong confidence inside Cambricon that it can secure those slots. Ultimately, the foundry’s capacity and yields will determine what any ramp-up looks like in practice.

Even if Cambricon clears the manufacturing hurdle, system integration presents its own bottleneck because AI accelerators require large pools of HBM to keep their compute units saturated. HBM3 and HBM3E are dominated by South Korean suppliers, and despite heavy investment, China has yet to produce a competitive domestic alternative. Huawei’s Ascend 910C, for example, still uses HBM stacks from SK Hynix and Samsung.

This is important because memory availability can limit the number of accelerators that can be deployed. Chinese cloud operators may secure sufficient chip volume but still face delays if they cannot pair those dies with matching HBM modules. With global demand rising across hyperscale data centers — which has arguably led to Micron disbanding its consumer business — neither capacity nor long-term supply for HBM is certain. Cambricon’s customers will need to lock in memory procurement early. Without that, it’s entirely possible that some fraction of the company’s planned 2026 output could sit idle until the right modules arrive.

Then there’s packaging. Multi-chiplet integration and high-speed interconnect routing all depend on advanced packaging lines. China’s capabilities have grown, but CoWoS-class technologies used by Nvidia, AMD, and TSMC remain out of reach for China. Cambricon must rely on what is available domestically, which dictates choices around chip partitioning and memory placement and influences both performance and scalability of the final accelerator boards.

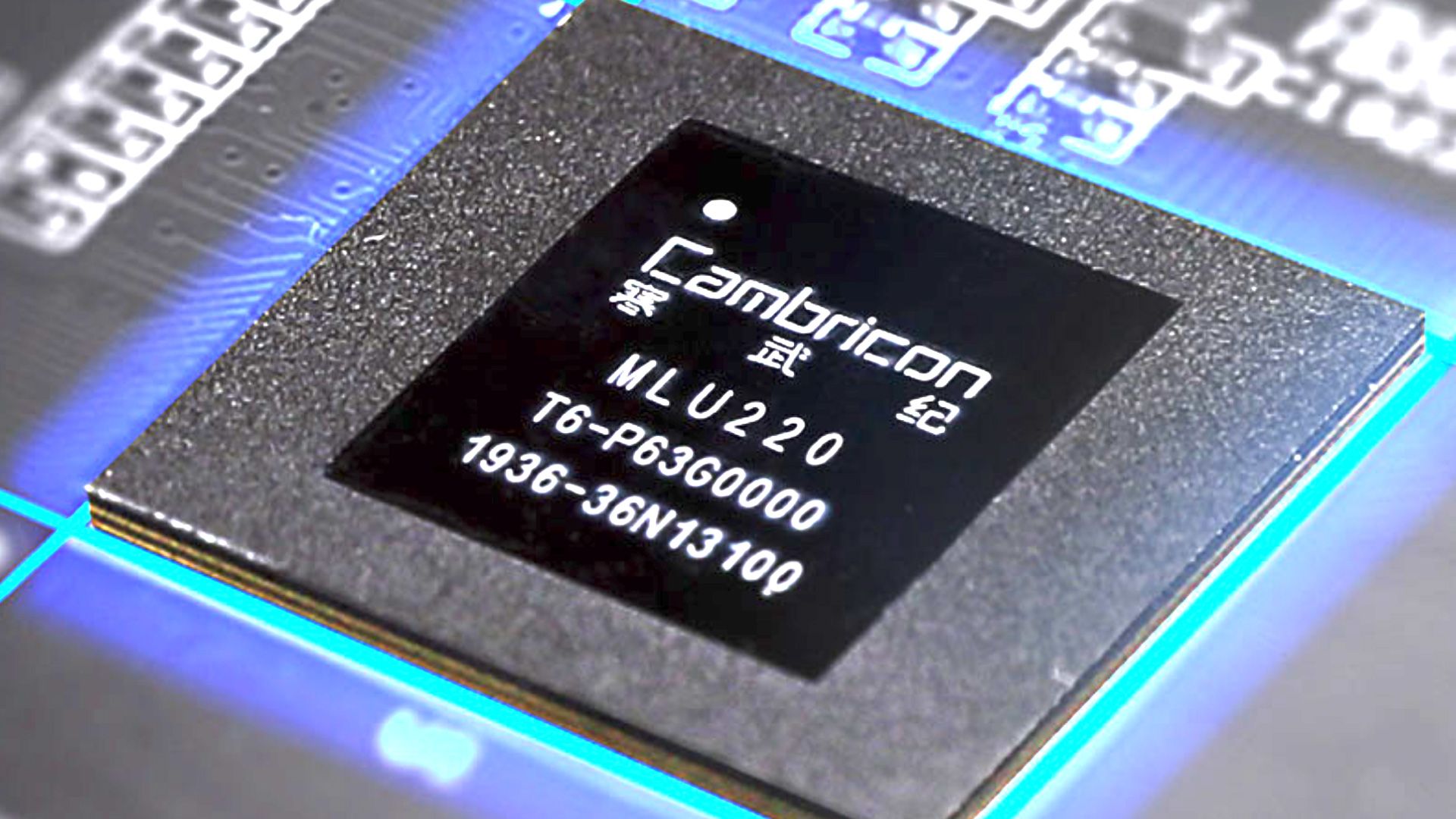

Chinese tech firm Cambricon looks to step into Nvidia void, triple AI chip production next year

Huawei Ascend NPU roadmap examined — company targets 4 ZettaFLOPS FP4 performance by 2028, amid manufacturing constraints

Huawei reveals long-range Ascend chip roadmap

Key considerations

- Investor positioning can change fast

- Volatility remains possible near catalysts

- Macro rates and liquidity can dominate flows

Reference reading

- https://www.tomshardware.com/tech-industry/semiconductors/SPONSORED_LINK_URL

- https://www.tomshardware.com/tech-industry/semiconductors/cambricon-targets-500000-ai-chips-in-2026-as-china-accelerates-domestic-hardware-push#main

- https://www.tomshardware.com

- At NeurIPS, NVIDIA Advances Open Model Development for Digital and Physical AI

- Dell preps massive price hikes up to 30% citing memory pricing 'out of our control' — company reminds commercial customers that placing an order today for futur

- Intel Core Ultra 7 270K Plus and Core Ultra 9 290K Plus spotted at Indian retailer — listings appear to corroborate prior leaks but don't reveal pricing or new

- CyberPower's Supreme gaming PC packs 64GB of DDR5-6400 RAM and an RTX 5080 GPU for $2499 — that's $700+ of RAM in today's market

- TSMC ponders upgrading 2nd Japan fab to 4nm — could pave the way for more advanced chips for Japanese customers (Updated)

Informational only. No financial advice. Do your own research.