ASML launches revolutionary lithography scanner for advanced 3D chip packaging — Twinscan XT:260 machine quadruples throughput

The solution jointly developed by Alchip and Ayar Labs is a three-chiplet co-packaged optical I/O subsystem that consists of an Alchip UCIe-A to UCIe-S protocol-converter chiplet that terminates the accelerator's UCIe-A interface and implements scale-up protocols (UALink, PCIe, Ethernet, SUE) over UCIe-S (streaming), an Alchip EIC that provides low-power SerDes, modulation drivers, clocking, and control, and an Ayar Labs TeraPHY PIC that performs the optical modulation and detection using silicon photonics.

The Alchip protocol converter can also carry non-UCIe protocols encapsulated over the UCIe physical interface, so it can work with compute dies that use proprietary protocols. The PIC uses a microring architecture and is delivered with detachable fiber connectors for manufacturability and offers two link options: PAM4 CWDM (100–200 ns per hop, BER < 10⁻⁶) and a DWDM fast-follower (20–30 ns per hop, BER < 10⁻¹²).

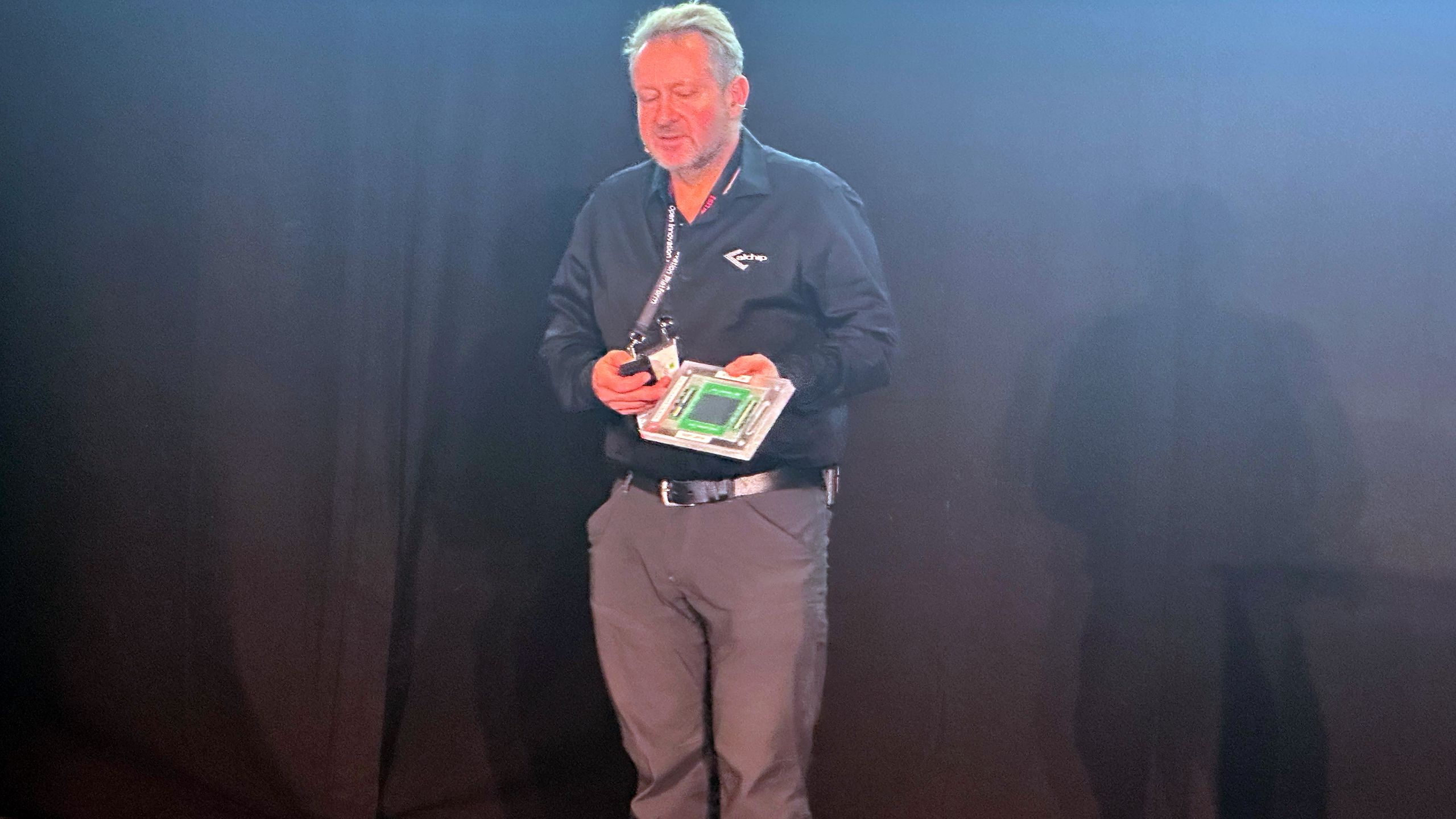

(Image credit: Alchip) (Image credit: Alchip) (Image credit: Alchip) (Image credit: Alchip) The optical subsystem can achieve extreme scale-up, supporting 100+ Tb/s of bandwidth per accelerator and 256+ optical ports per device to connect hundreds of processors across multiple racks and operate them as a single large processor. Alternatively, the companies envision that their solution could be used for memory extenders as well.

The reference design (a mockup) includes two full-reticle accelerator dies, eight HBM stacks, four protocol-converter chiplets, and eight Ayar Labs TeraPHY optical engines, all mounted on a single substrate with integrated passive devices for power integrity. Alchip's system diagrams demonstrate the platform connecting XPU-to-XPU, XPU-to-switch, and switch-to-switch, and even enabling optical memory expansion.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Key considerations

- Investor positioning can change fast

- Volatility remains possible near catalysts

- Macro rates and liquidity can dominate flows

Reference reading

- https://www.tomshardware.com/tech-industry/semiconductors/SPONSORED_LINK_URL

- https://www.tomshardware.com/tech-industry/semiconductors/industrys-first-tsmc-coupe-based-optical-connectivity-solution-for-next-gen-ai-chips-displayed-alchip-and-ayar-labs-show-future-silicon-photonics-device#main

- https://www.tomshardware.com

- NVIDIA Accelerates AI for Over 80 New Science Systems Worldwide

- Grab a 49-inch OLED ultrawide monitor at Amazon UK for less than £700 — MSI MPG 491CQP drops to lowest-ever price

- Chinese vendor showcases first mass-produced Imagination DXD GPU with ray tracing — sports modern features like super resolution, too

- Save up to $350 on RTX 5050-equipped Acer Nitro V gaming laptops this Cyber Monday — Grab a 16-inch AMD variant for just $629, or an Intel 15-incher for $579

- Accelerated Computing, Networking Drive Supercomputing in Age of AI

Informational only. No financial advice. Do your own research.