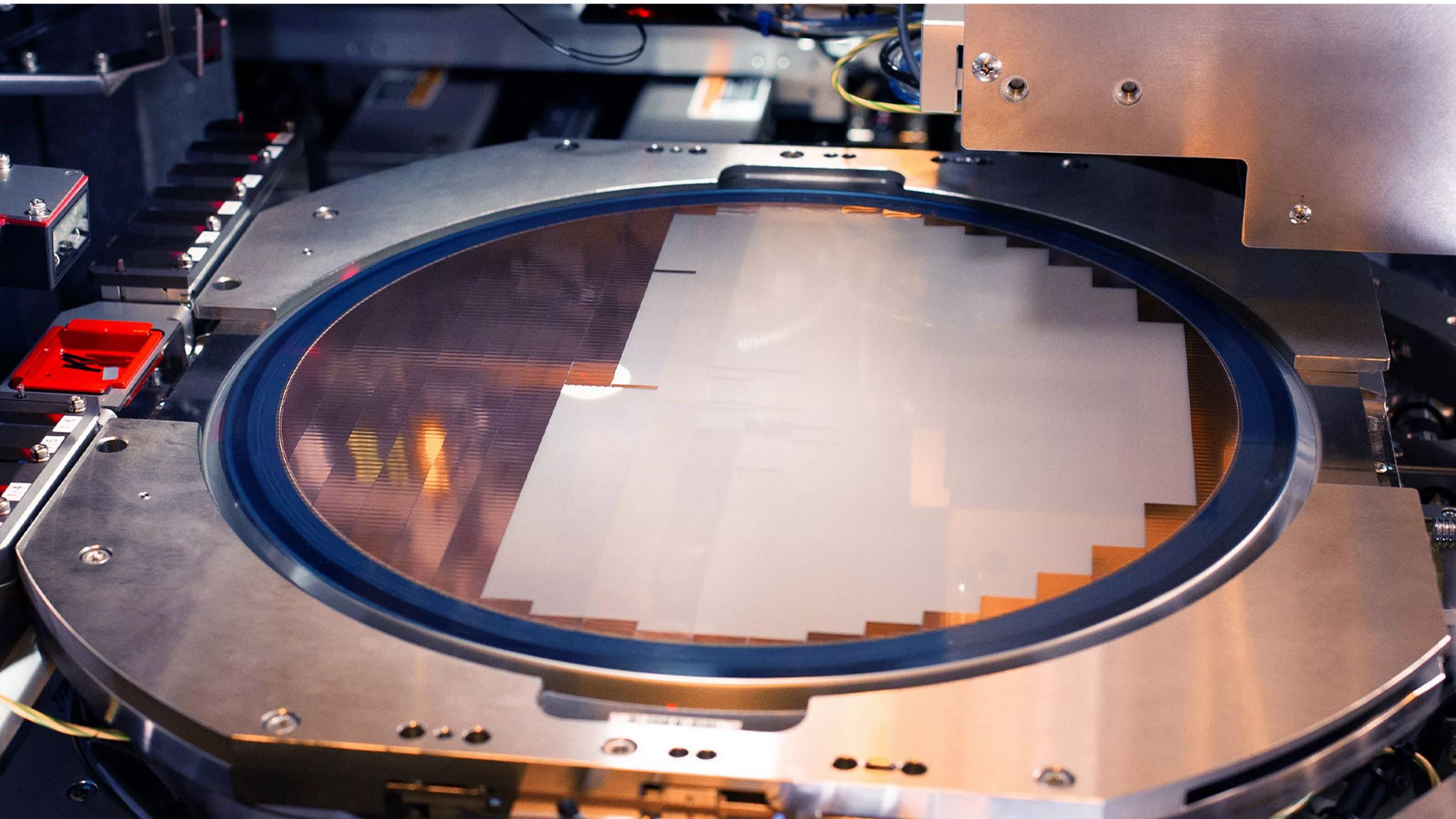

Note that the video Intel Foundry posted on X shows two conceptual designs: a 'mid-scale' one featuring four compute tiles and 12 HBM, and an 'extreme' one with 16 tiles and 24 HBM5 stacks, which our story focuses on. Even the mid-scale design is fairly advanced by today's standards, but Intel can produce it today.

As for the extreme concept, this may emerge toward the end of the decade, when Intel has perfected not only Foveros Direct 3D packaging technology but also its 18A and 14A production nodes. Being able to produce such extreme packages towards the end of the decade will put Intel on par with TSMC, which plans something similar and even expects at least some customers to use its wafer-size integration offerings in circa 2027 – 2028.

Making the extreme design a reality in just a few years is a significant challenge for Intel, as it must ensure the components do not warp when attached to motherboards and do not deform even with minimal tolerances due to overheating after prolonged use. Beyond that, Intel (and the whole industry) will need to learn how to feed and cool monstrous processor designs the size of a smartphone (up to 10,296 mm^2) that will have an even larger package, but that's a different story.

Follow Tom's Hardware on Google News , or add us as a preferred source , to get our latest news, analysis, & reviews in your feeds.

Anton Shilov Social Links Navigation Contributing Writer Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

Key considerations

- Investor positioning can change fast

- Volatility remains possible near catalysts

- Macro rates and liquidity can dominate flows

Reference reading

- https://www.tomshardware.com/tech-industry/semiconductors/SPONSORED_LINK_URL

- https://www.tomshardware.com/tech-industry/semiconductors/intel-displays-tech-to-build-extreme-multi-chiplet-packages-12-times-the-size-of-the-largest-ai-processors-beating-tsmcs-planned-biggest-floorplan-the-size-of-a-cellphone-armed-with-hbm5-14a-compute-tiles-and-18a-sram#main

- https://www.tomshardware.com

- China chipmaker SMIC raises wafer prices by about 10% as memory demand tightens capacity

- Microsoft promises to nearly double Windows storage performance after forcing slow software-accelerated BitLocker on Windows — new CPU hardware-accelerated cryp

- Starlink satellite pictured ‘tumbling’ after recent ‘anomaly’ in space — it will be incinerated when it enters the Earth’s atmosphere in a few weeks

- Samsung to delay its planned DDR4 end-of-life due to signing a long-term 'non-cancellable, non-returnable' contract with key customer — agreement will not allev

- Now Generally Available, NVIDIA RTX PRO 5000 72GB Blackwell GPU Expands Memory Options for Desktop Agentic AI

Informational only. No financial advice. Do your own research.