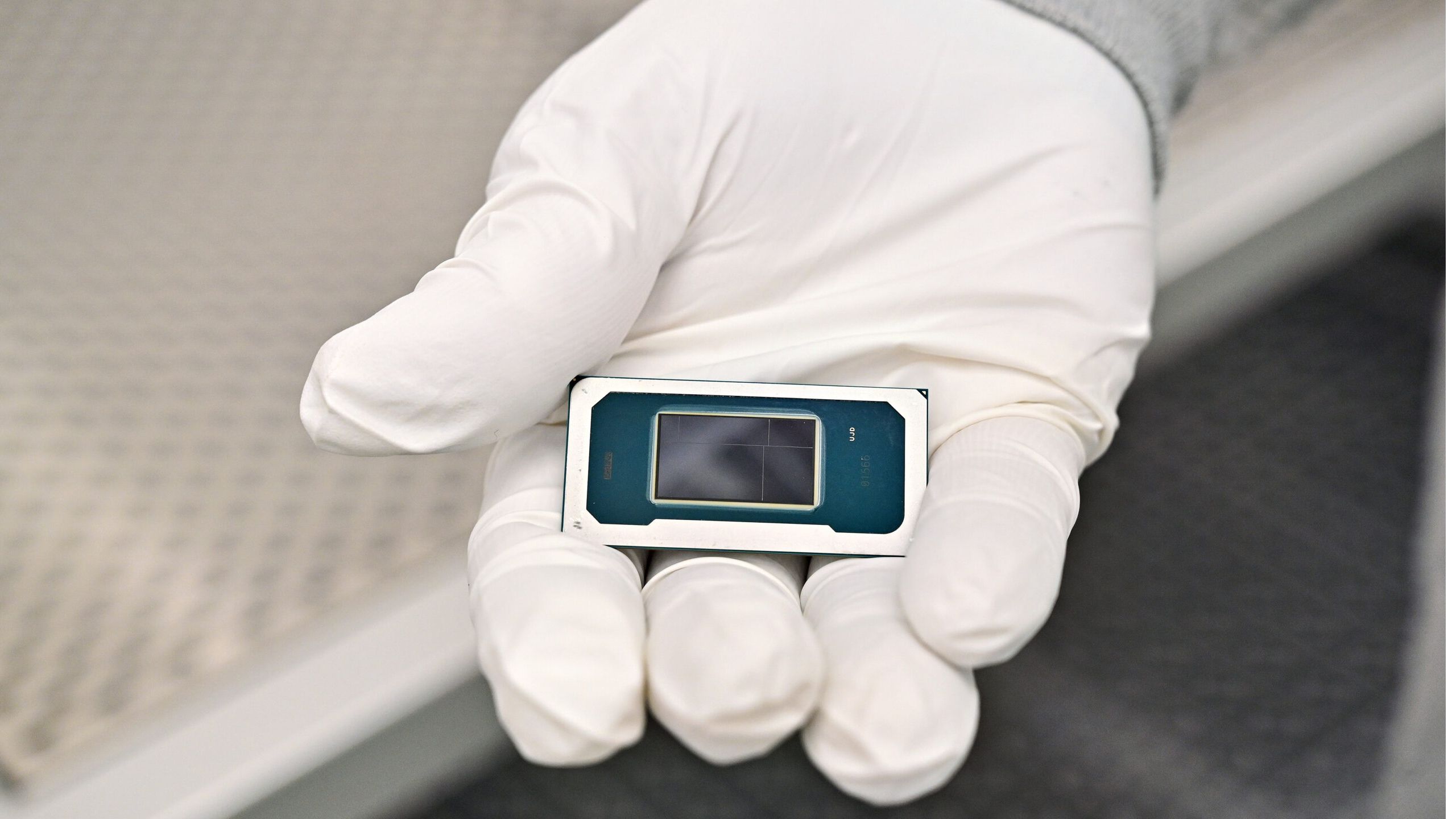

Panther Lake-H's compute tile (or system-on-chip tile, as Kurnal calls it) integrates four high-performance Cougar Cove cores with 3 MB L2 cache designed to run at up to 5.1 GHz. In addition, the main compute tile also packs eight space-efficient Darkmont cores running at up to 3.8 GHz and four low-power Darkmont cores operating at up to 3.7 GHz. As far as we can tell, there are no physical differences between Darkmont E-core cluster with 4 MB L2 cache and Darkmont LPE-core cluster with 4 MB L2 cache. Yet, the 18 MB L3 cache split into three slices to serve nearby cores faster is located close to the P-core and E-core clusters, far away from the LPE cluster. NPUs — split into three slices — also have their own 4.5 MB of cache.

Splitting L3 and NPUs into slices enables Intel to disable a defective slice without affecting others in a bid to get a sellable die, albeit offering lower performance.

You may like Intel doubles down on gaming with Panther Lake, claims 76% faster gaming performance Intel Nova Lake die sizes leak, signaling higher cost Intel Panther Lake press Q&A transcript — EVO is still alive, and the company ditches prior-generation naming scheme Intel Panther lake-H DieshotThanks by 万扯淡 Decaphigh pixel Dieshot in my websitehttps://t.co/SOHGS0eViBCPU 14.32×8.04×0.18mmGPU 8.14×6.78×0.2mmIOD 12.44×4.00×0.18mmKurnal will try to change the CPU Die pic.twitter.com/Bmp6Iomlz7 March 5, 2026

What is interesting is that the 128-bit DDR5/LPDDR5X-9600 memory controller also has an 8MB memory side cache (MSC), which job is to buffer memory traffic and reduce latency/bandwidth pressure when many cores (or other execution units inside the compute tile, such as NPUs) access RAM simultaneously. Panther Lake is not Intel's first use of a memory-side cache–type structure, though earlier concepts (e.g., CrystalWell L4 cache) were implemented in a considerably different way and their purpose has evolved over time. Therefore, we cannot compare Panther Lake's memory side cache to Apple's system-level cache, which acts like the last level cache for the whole SoC, which is not the case with Intel's MSC.

Another interesting feature of the compute tile are the integrated media and display engines. Such an arrangement enables Intel to attach various GPUs and I/O dies while maintaining key functionality inside the compute tile, which provides the company some additional flexibility with CPU configurations.

In general, the compute tile resembles Intel CPUs released in the recent years, which almost certainly means ring bus interconnect. Yet, the SoC tile also has high-performance interfaces that connect to GPU and I/O die tiles.

As for the GPU tile, it integrates 12 Intel Xe3 clusters and 16MB of L2 cache implemented in eight tiles, which again allows Intel to disable faulty GPU clusters or cache tiles to improve yield of sellable chips.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Key considerations

- Investor positioning can change fast

- Volatility remains possible near catalysts

- Macro rates and liquidity can dominate flows

Reference reading

- https://www.tomshardware.com/pc-components/cpus/SPONSORED_LINK_URL

- https://www.tomshardware.com/pc-components/cpus/intel-panther-lake-h-high-res-die-shot-emerges-image-show-18a-compute-tile-xe3-gpu-tile-in-new-x-series-processors#main

- https://www.tomshardware.com

- Scientists attempt to link 3D printed ghost guns to specific filament brands with chemical fingerprinting — major filament makers often white-label products, co

- Thermal Grizzly scammed out of $46,000 by Alibaba metals suppliers — company spread the risk across two copper and aluminum suppliers, only for both to send che

- Jensen Huang set to receive $4 million bonus from Nvidia, 0.002% of his $164 billion net worth — a small incentive for one of the richest people on earth

- Save $484 on a Ryzen 7 9850X3D, 32GB of Kingston DDR5 RAM, and an Asus X870 motherboard — start your AM5 build on the right foot with this $949 bundle

- The best Amazon UK Spring Deals Days tech sales 2026 — featuring the best prices on the latest gaming PCs, GPUs, laptops, monitors, peripherals, and more

Informational only. No financial advice. Do your own research.