Canon, which has long argued that the industry needs an alternative, offers a nanoimprint lithography (NIL) system that patterns wafers by stamping a pre-formed template directly into resist rather than projecting a pattern optically. That equipment can be priced much lower than EUV, and Canon has claimed that the technology uses up to 90% less power. Just last year, the company delivered its first commercial FPA-1200NZ2C tool to the Intel- and Samsung-backed Texas Institute for Electronics, 20 years after NIL research began.

NIL has been looked upon with some skepticism in recent years due to its incompatibility with both DUV and EUV, and the more conventional view that NIL could not meet the overlay stability or defectivity requirements needed for tightly packed logic at sub-2nm geometries. DNP’s new template material is the first attempt to challenge that assumption with concrete specifications and a timeline to commercialization.

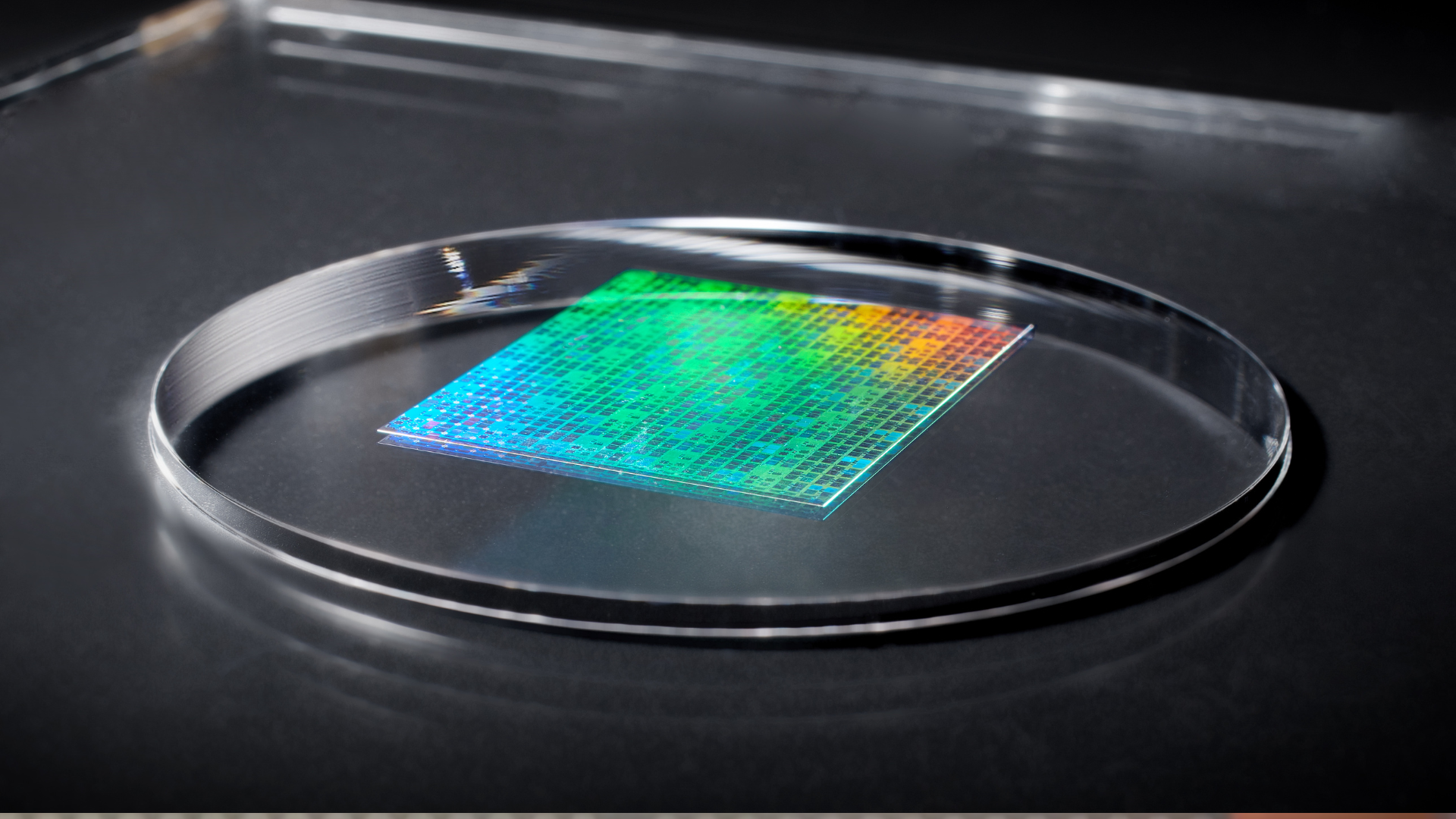

DNP’s template reportedly achieves 10nm line widths and is being evaluated ahead of planned mass production in 2027. Meanwhile, TSMC’s 1.4nm-class node is scheduled for risk production in the same year, with broader output in 2028 , and Samsung has targeted a similar window. Both companies are expected to rely on EUV for the majority of patterning steps, but neither will be blind to the cost pressures. A secondary patterning pathway that reduces EUV load would be welcome, provided it clears the engineering hurdles.

Canon has pitched nanoimprint not as a replacement for EUV but as a complementary tool for specific layers and structures. Advanced patterning at sub-2nm often relies on techniques such as self-aligned double and quadruple patterning to extend resolution beyond single-exposure limits, and some researchers have explored how alternative lithography approaches, such as NIL, fit into these schemes. Nobody is claiming that a 1.4nm chip can be manufactured entirely through imprinting; rather, the proposal is that certain layers, currently exposed with EUV, could be transferred to a lower-cost, lower-power workflow.

That could have important ramifications for cost control, as every EUV step adds both energy consumption and process time. If a handful of those can be replaced by nanoimprint without sacrificing uniformity or yield, fabs gain extra flexibility. And when we’re talking about a 1.4nm production line churning tens of thousands of wafers per month, even marginal reductions in EUV dependency could translate to huge savings.

If DNP’s template can achieve the required precision for 1.4nm logic, the largest remaining obstacle is manufacturing scale. Imprint relies on a mechanical master pattern that must remain dimensionally perfect throughout its life. Even slight abrasion or contamination forces a replacement, and templates are both expensive and slow to produce. Running nanoimprint at volume will therefore necessitate a reliable supply of near-perfect masters and a way to verify their integrity rapidly enough to avoid passing defects downstream.

Advanced logic layers also require alignment precision on the order of a few nanometers across a 300 mm wafer. Achieving that through an act of mechanical contact is orders of magnitude more demanding than aligning an optical projection. Canon’s system tackles this with a step-and-repeat approach and local deformation control, but real-world results have yet to be demonstrated on the layers where tolerances are tightest.

American startup Substrate promises 2nm-class chipmaking with particle accelerators, at a tenth of the cost of EUV

Chinese scientists discover method to cut defects by 99% with DUV chipmaking equipment

Russia outlines EUV litho chipmaking tool roadmap through 2037

Key considerations

- Investor positioning can change fast

- Volatility remains possible near catalysts

- Macro rates and liquidity can dominate flows

Reference reading

- https://www.tomshardware.com/tech-industry/semiconductors/SPONSORED_LINK_URL

- https://www.tomshardware.com/tech-industry/semiconductors/japans-dnp-targets-2027-mass-production-of-1-4nm-nanoimprint-templates#main

- https://www.tomshardware.com

- Trump secures deal with Korea Zinc to build rare earths processing facility in Tennessee — facility expected to have annual output of 540,000 tons of gallium, g

- Lenovo's powerful Steam Deck rival handheld just hit a record-low price on Amazon UK — 8-inch Legion Go S running SteamOS now under £428, with 16GB RAM and 1TB

- 2,800 RGB drones turned into the world's largest-ever game of Tetris — Red Bull Tetris world final lights up Dubai night sky

- Boy breaks 50 of his father's Samsung M.2 NVMe SSDs worth nearly $4,000 — 25,600 GB of storage ruined by ten-year-old oblivious to global NAND crisis

- Arctic launches its best thermal paste yet for chips of all types — claims new MX-7 formulation runs 3% cooler than its predecessor

Informational only. No financial advice. Do your own research.