Next-gen memory designed as a lower-cost, lower-power HBM alternative for AI workloads

When you purchase through links on our site, we may earn an affiliate commission. Here’s how it works .

NEO Semiconductor announced on April 23rd that its 3D X-DRAM technology has successfully passed proof-of-concept (POC) validation, demonstrating that a new class of high-density DRAM can be manufactured using existing 3D NAND infrastructure. The company simultaneously announced a new strategic investment led by Stan Shih, founder and former Chairman and CEO of Acer, and a board director of TSMC for over two decades.

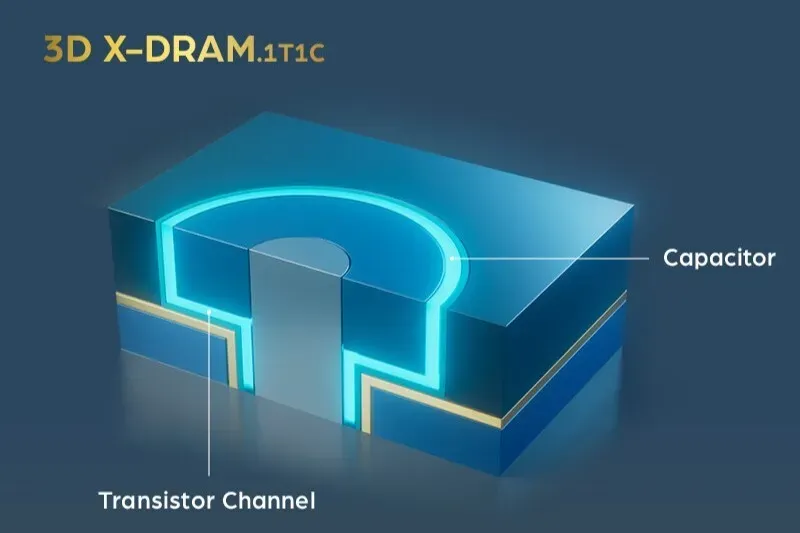

At the center of the announcement is the company’s 3D X-DRAM technology , a new class of DRAM that aims to break past conventional memory scaling limits by adopting a vertically stacked architecture designed for higher density, lower power consumption, and improved suitability for AI-driven workloads.

You may like SoftBank subsidiary working with Intel to develop radical new ZAM memory is now receiving Japanese gov't subsidies Intel is co-developing new Z-Angle Memory to compete with HBM used in AI data centers Memory makers are set to earn $551 billion from the AI boom, twice as much as contract chip manufacturers The proof-of-concept chips, fabricated and tested at Taiwan's National Institutes of Applied Research – Taiwan Semiconductor Research Institute (NIAR-TSRI) in collaboration with National Yang Ming Chiao Tung University, delivered the following results: Read/write latency : under 10 nanoseconds Data retention : over 1 second at 85°C/185°F (claimed 15× improvement over JEDEC standard) Bit-line disturbance : over 1 second at 85°C (185°F) Word-line disturbance : over 1 second at 85°C Endurance : greater than 10¹⁴ cycles

"These results validate a new scaling path for DRAM," said Andy Hsu, Founder & CEO of NEO Semiconductor. "We believe this technology can enable significantly higher density, lower cost, and improved energy efficiency for the AI era. By leveraging established 3D NAND manufacturing processes and ecosystem, we aim to bring 3D DRAM to reality sooner. NEO is actively engaging with leading global memory and semiconductor companies on potential co-development opportunities, and we believe our technology is well suited for a scalable licensing and partnership model to bring next-generation AI memory solutions to market."

Industry commentary included in the announcement was quite positive — although this does not imply confirmation of viability at scale. TechInsights’ Jeongdong Choe described the results as a “significant milestone” in the shift toward 3D memory architectures, noting that conventional DRAM scaling is approaching physical limits and that the industry is increasingly exploring vertical alternatives.

The broader context behind this development is the growing strain AI workloads are placing on memory systems. While GPU compute performance has scaled aggressively over the past decade, memory bandwidth — the rate at which data can be fed to those processors — has become a limiting factor in large-scale AI training and inference systems. This has already driven widespread adoption of high-bandwidth memory (HBM), a vertically stacked DRAM architecture integrated close to GPUs. However, HBM presents complex 3D stacking and bonding requirements and high manufacturing costs.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Key considerations

- Investor positioning can change fast

- Volatility remains possible near catalysts

- Macro rates and liquidity can dominate flows

Reference reading

- https://www.tomshardware.com/tech-industry/artificial-intelligence/SPONSORED_LINK_URL

- https://www.tomshardware.com/tech-industry/artificial-intelligence/neo-semiconductors-revolutionary-3d-x-dram-for-ai-processors-has-passed-proof-of-concept-validation-company-secures-funding-to-develop-next-gen-memory-hbm-alternative#main

- https://www.tomshardware.com/subscription

- Samsung engineer sentenced to 7 years in prison for selling chipmaking trade secrets to Chinese chipmaker — ex-employee supplied 10nm DRAM data to CXMT for $2 m

- Amazon Eero and Leo routers gain FCC Conditional Approval for US sales — Eero products can skirt router ban for the next 18 months, firm joins Netgear on approv

- Alienware Area-51 gaming desktop now available with AMD’s flagship Ryzen 9 9950X3D2 Dual Edition — top CPU config starts at $4,449.99 with RTX 5070 and 32GB DDR

- OpenAI’s New GPT-5.5 Powers Codex on NVIDIA Infrastructure — and NVIDIA Is Already Putting It to Work

- Anthropic surpasses biggest rival OpenAI in secondary market valuation — surges to $1 trillion amid frantic investor interest

Informational only. No financial advice. Do your own research.