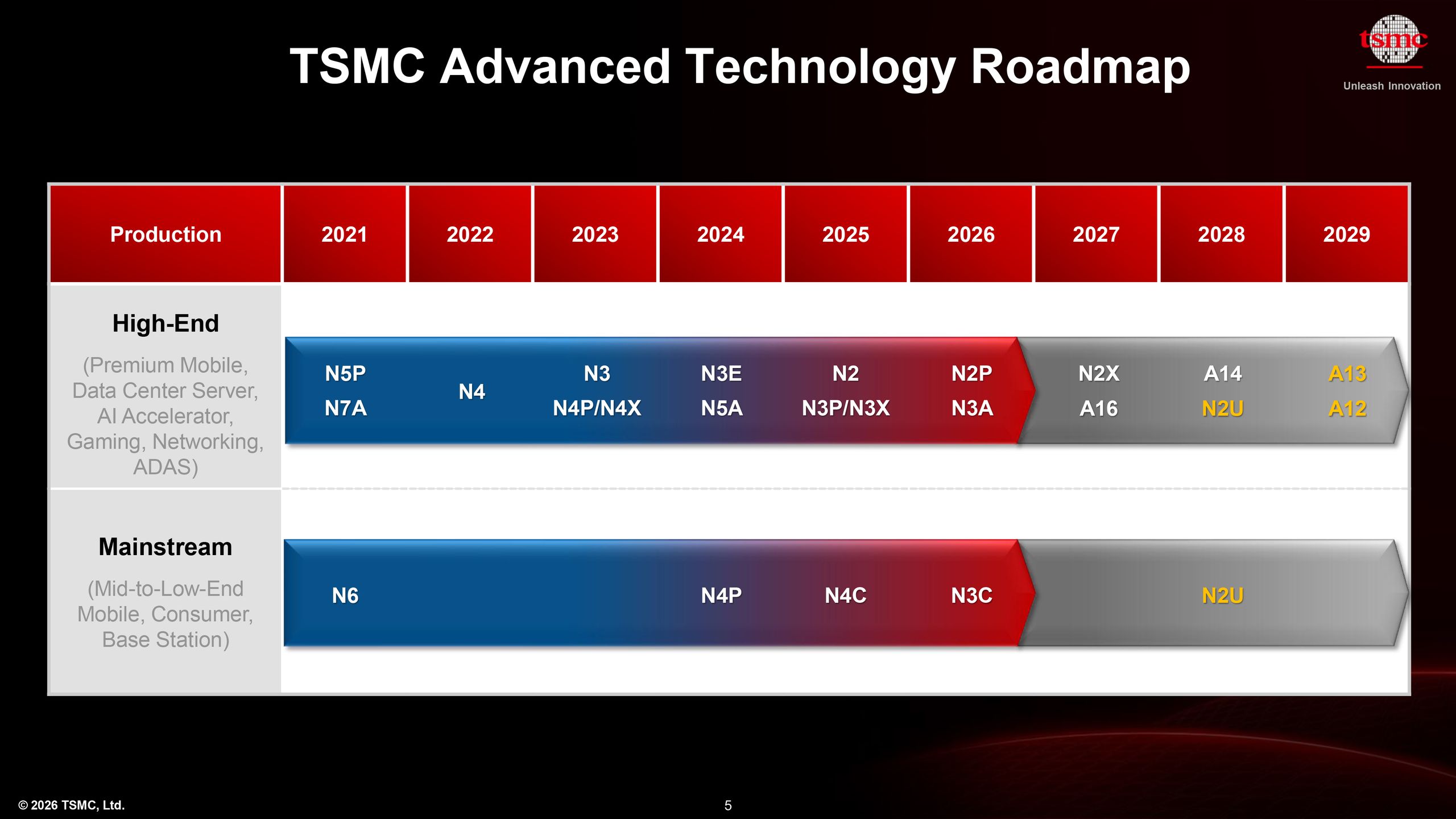

While TSMC's N2 is set to be adopted both for client and data center applications, the company preps A16 with its Super Power Rail backside power delivery that is specifically tailored for high performance data center applications. Essentially, A16 is N2P with SPR that will rely on the 1 st Generation nanosheet GAA transistors and provide significant power, performance, and transistor density advantages over N2 and N2P nodes, albeit at higher cost. It is noteworthy that TSMC now lists A16 as a 2027 process technology, which is technically a slip from 2026. "A16 will be ready for production in 2026," Zhang said. "However, actual product ramp depends on customers, and we expect volume production to begin in 2027. That is why we aligned it to that timeline." Interestingly, the arrival of A16 does not replace N2X, a performance-enhanced variant of N2P that uses traditional front side power delivery to push clocks of N2-based designs to the max. A16 will pass the baton to A12 — set to arrive in 2029 — which is projected to bring full-node advantages to TSMC's data center-class nodes. While TSMC does not disclose actual numbers, expect A12 to offer the same kinds of benefits over A16 as A14 brings over N2 as it is set to rely on the company's 2 nd Gen nanosheet GAA transistors and NanoFlex Pro technology. "A16 is our 1 st Generation technology with super power rail — the backside power," Zhang said. "A12 is the next generation […] to continue to shrink both frontside and backside to achieve overall density benefit."

One interesting thing to note about TSMC's upcoming A13 and A12 process technologies due in 2029 is that none of them will require High-NA EUV lithography tools, which is stark contrast to Intel's approach to its 14A production node and successors that are set to use High-NA EUV scanners starting in 2027 – 2028. "I tell you, I am amazed by our R&D team," said Kevin Zhang. "They continue to find a way to drive the technology scaling without using High-NA. One day they may have to use it, but at this point, we continue to be able to harvest the benefit from current EUV, not have to go to High-NA, which, you know, very, very expensive."

Follow Tom's Hardware on Google News , or add us as a preferred source , to get our latest news, analysis, & reviews in your feeds.

Anton Shilov is a contributing writer at Tom\u2019s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends. ","collapsible":{"enabled":true,"maxHeight":250,"readMoreText":"Read more","readLessText":"Read less"}}), "https://slice.vanilla.futurecdn.net/13-4-20/js/authorBio.js"); } else { console.error('%c FTE ','background: #9306F9; color: #ffffff','no lazy slice hydration function available'); } Anton Shilov Social Links Navigation Contributing Writer Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

usertests Under N2U vs N2P: "8% – 10%" should be "-8% ~ -10%" to match the other columns indicating reductions. Reply

usertests I guess "N2U" is what passes for a budget node like N4C(heap). Not sure why they dropped the "C". Hopefully, SPR / backside power delivery becomes standard at some point after A12. A14's mixed 1.2x "chip density" gain is not much less than the 1.23x logic density gain. Maybe this indicates it will be a great node for SRAM scaling, from the "2nd gen" GAAFET transistors. I'm surprised this aspect wasn't commented on before. We have a leak of Zen 7 using ~98mm^2 Silverton chiplets with 16 cores, 2 MiB L2 cache per core, and 64 MiB L3 cache on the A14 node. If SRAM density is up 10-15% on that node, that could be the only thing preventing the chiplet from swelling to over 100mm^2. Reply

Key considerations

- Investor positioning can change fast

- Volatility remains possible near catalysts

- Macro rates and liquidity can dominate flows

Reference reading

- https://www.tomshardware.com/tech-industry/semiconductors/SPONSORED_LINK_URL

- https://www.tomshardware.com/tech-industry/semiconductors/tsmc-unveils-process-technology-roadmap-through-2029-a12-a13-n2u-announced-a16-slips-to-2027#main

- https://www.tomshardware.com

- Strength and Destiny Collide: ‘Samson: A Tyndalston Story’ Arrives in the Cloud

- Every SK hynix employee could receive $477,000 bonuses this year, almost $900,000 next year — 35,000 workers reportedly set to benefit from share of $169 billio

- Voyager 1 gets emergency instrument shutdown to solve escalating power crisis and give it ‘about a year of breathing room’ — interstellar spacecraft's nuclear p

- Framework’s overhauled Laptop 13 Pro brings a redesigned chassis — Intel Core Ultra Series 3 system aims to be a 'MacBook Pro for Linux users'

- Save a huge $460 on this RTX 5080 gaming PC with a 9800X3D, 32GB of DDR5 RAM, and a 2TB SSD — $3,039.99 sale price nets you this Newegg ABS pre-built powerhouse

Informational only. No financial advice. Do your own research.